Après avoir étudié des configurations de circuits propres aux mondes analogiques et numériques, il est naturel de vouloir les interfacer.

Les convertisseurs numériques - analogiques (CNA - DAC en Anglais) et analogiques - numériques (CNA - ADC en Anglais) permettent cette navigation entre les deux mondes.

Plusieurs solutions de CNA et CAN seront analysées et comparées.

En annexe nous proposons quelques définitions complémentaires, ainsi que l'analyse d'une cellule fondamentale la paire différentielle, utilisée dans le monde des convertisseurs pour jouer le rôle de switch analogique (interrupteur analogique).

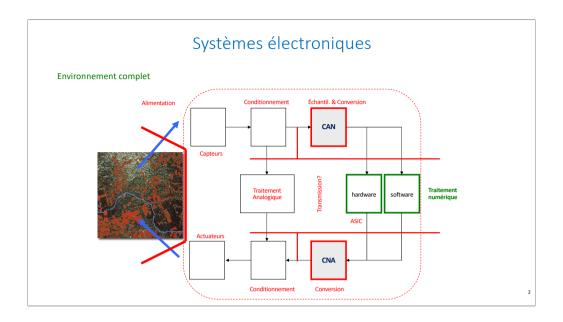

Nous avons évoqué en début d'année, la volonté de l'être humain de maîtriser la nature. D'acquérir ses manifestations dans le but de les analyser afin de reproduire ou de transformer les phénomènes. L'électronique au sens large contribue à cette maîtrise.

Les traitements sont généralement associés à des réflexions à caractères algorithmiques qui suggèrent deux types de réalisation:

- des circuits numériques spécifiques aux traitements

- des circuits standards (microprocesseur, mémoire) dont le comportement est enrichi par une couche logicielle.

La nature étant par définition analogique, il faut donc interfacer à l'aller comme au retour, les signaux qui sont véhiculés dans ces deux mondes.

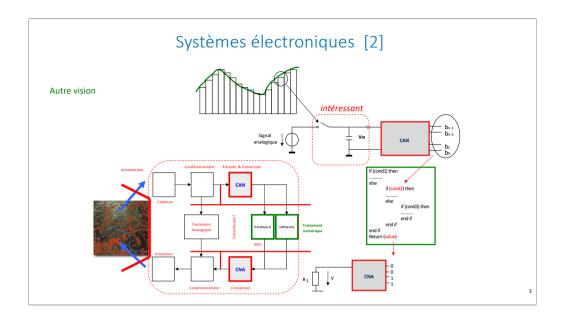

Une vision plus précise montre que le signal analogique doit être échantillonné.

En effet, la nature évolue de manière continue, alors que le traitement informatique doit travailler dans le mode discret qui plus est, avec des fréquences non infinies.

Selon le degré de précision souhaité du phénomène traité et des limites de performances des circuits, le nombre d'échantillons prélevés sera plus ou moins important.

Il est clair que le temps qui sépare le prélèvement de deux échantillons doit permettre de traiter (de manière algorithmique) chaque échantillon.

On distinguera donc deux fréquences, respectivement la fréquence d'échantillonnage et celle de traitement.

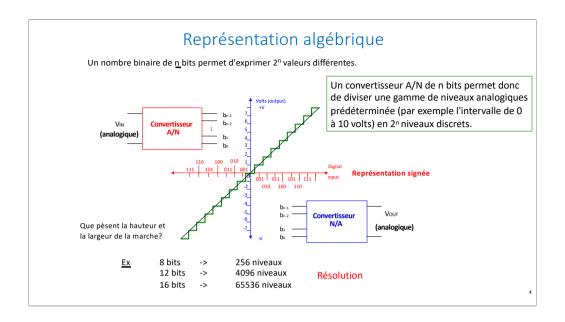

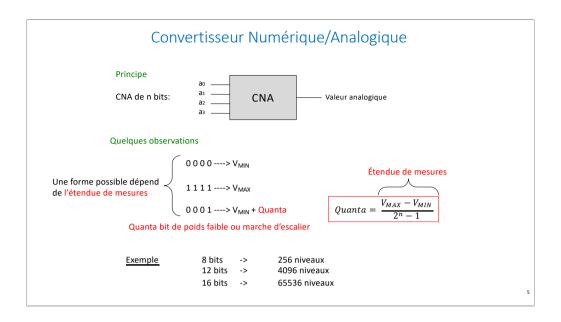

La figure ci-dessus illustre l'importance du codage binaire dans la précision des échantillons traités.

Imaginons que le phénomène analysé soit transformé en grandeur électrique (une tension), dont la dynamique varie entre 0V et 10V.

Nous voyons que la précision de l'échantillon converti en valeur binaire dépend du nombre de bits de représentation (résolution).

Ainsi avec 8 bits, on obtiendrait 256 niveaux correspondant à 256 valeurs de tension comprises entre 0V et 10V, soit une précision de 10/256 ~40 mV.

Avec 12 bits, on obtiendrait 4096 niveaux correspondant à 4096 valeurs de tension comprises entre 0V et 10V, soit une précision de  $10/4096 \sim 2.5$  mV.

Avec 16 bits, on obtiendrait 65536 niveaux correspondant à 65536 valeurs de tension comprises entre 0V et 10V, soit une précision de  $10/65536 \sim 160 \mu V$ .

On propose les définitions suivantes:

- •Lorsque tous les bits représentatifs de l'échantillon sont à 0, alors il s'agit de la tension minimale  $V_{MIN}$  (on prendra souvent  $V_{MIN}$ = 0V)

- •Lorsque tous les bits représentatifs de l'échantillon sont à 1, alors il s'agit de la tension maximale  $V_{\rm MAX}$

La précision de l'échantillon est mise en évidence avec le bit de poids faible. Cette précision s'appelle le Quanta.

• Lorsque seul le bit de poids faible vaut 1, alors la valeur binaire représente  $V_{\mbox{\scriptsize MIN}}$  + Quanta.

Le Quanta peut s'exprimer aussi à partir de la dynamique analysée ( $V_{MAX}$  -  $V_{MIN}$ ) et du nombre d'échantillons distincts que l'on peut représenter. Sur n bits, on aura  $2^n$  - 1 intervalles et le Quanta vaut ( $V_{MAX}$  - $V_{MIN}$ )/( $2^n$ -1)

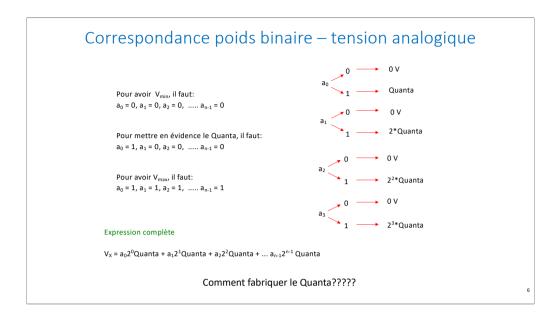

Pour simplifier l'analyse, on admet que l'on travaille avec une dynamique allant de  $V_{MIN}=0V$  à  $V_{MAX}$ , que l'on souhaite représenter sur 4 bits.

Si le Quanta est représenté par le bit de poids faible (a<sub>0</sub>), alors le second bit (a<sub>1</sub>) de poids faible représente deux fois le Quanta.

Le troisième bit  $(a_2)$  vaudra le double du second soit 4 fois le Quanta  $(2^2)$  et le quatrième bit  $(a_3)$  vaudra encore le double du précédent soit 8 fois le Quanta  $(2^3)$ .

Chaque bit valant 0 ou 1, la représentation binaire correspond à une somme de puissances de 2, la tension représentant la valeur binaire est obtenue directement en multipliant la valeur binaire par le Quanta.

Dans la réalité, les valeurs analogiques ne seront pas obtenues par cumul de valeurs proportionnelles au Quanta (l'erreur serait trop grande), mais plutôt par un partitionnement d'une valeur de référence dont l'ordre de grandeur sera comparable à  $V_{\rm MAX}$ .

# Expression générale

$$V_{\rm OUT} = a_0 2^0 {\rm Quanta} + a_1 2^1 {\rm Quanta} + a_2 2^2 {\rm Quanta} + \dots \\ a_{n-1} 2^{n-1} {\rm Quanta}$$

$$Quanta = \frac{V_{REF}}{2^n}$$

$$V_{OUT} = \frac{1}{2^n} . V_{REF} [a_0 2^0 + a_1 \ 2^1 + \dots \\ a_{n-2} 2^{n-2} + a_{n-1} 2^{n-1}]$$

$a_0$  = bit de poids le plus faible ou LSB (lower significant bit)  $a_{n-1}$  = bit de poids le plus fort ou MSB (most significant bit)

Valeur maximale de V<sub>OUT</sub>

On admet ici que V<sub>MIN</sub> = 0V

$V_{OUT\_MAX} = \frac{2^n - 1}{2^n} V_{REF}$

Nous proposons une expression générale, qui rappelle structurellement la précédente, et qui sera exploitée dans les montages étudiés par la suite.

- V<sub>REF</sub> est une tension de référence qui imposera la dynamique du circuit.

- n est le nombre de bits de précision

- $\bullet$   $b_i$  est le bit dont le poids est en (i+1)ème position

- ullet  $b_0$  est le bit de poids le plus faible

- $\bullet$   $b_{n\text{-}1}$  est le bit de poids le plus fort

On détermine aisément  $V_{MAX} = (2^n - 1) \cdot V_{REF}/2^n$  (tous les bits sont à 1) et Quanta =  $V_{REF}/2^n$  seul le bit de poids faible est à 1.

J'utilise des a à la place des b pour marquer la différence entre la réalisation et le concept algébrique

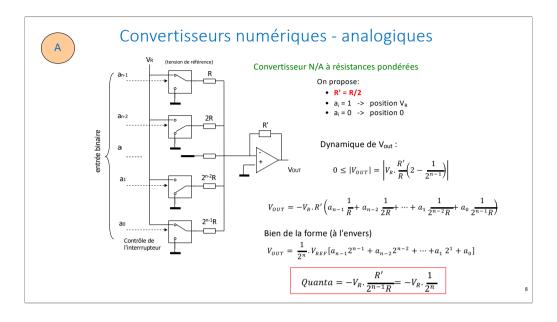

Le convertisseur numérique analogique le plus simple est réalisé avec des résistances pondérées.

Le montage global rappelle un sommateur où les entrées valent soit 0V soit une pondération d'une tension de référence.

Les valeurs de résistances correspondent à des puissances de 2 fois une résistance de base  $R^\prime\!=R/2$

Chaque résistance est connectée soit à la tension de référence  $V_{\text{REF}}$ , soit à la masse, selon que la valeur binaire  $a_i$  qui la contrôle vaut 1 ou 0.

En sommant les différentes valeurs de  $V_{REF}$  pondérée, on obtient une formule représentant  $V_{OUT}$  correspondant très précisément à celle mise en évidence dans l'expression générale. Il en est de même pour la valeur du Quanta.

# Convertisseur N/A à résistances pondérées

### Précision-stabilité

La précision de ce convertisseur dépend de la précision du rapport des résistances et du maintien de ce rapport en fonction du temps et de la température.

### Exemple:

pour un convertisseur 8 bits, la résistance de poids le plus élevé vaut R et celle de poids le plus faible vaut R  $2^{n-1}$  = 128 R.

Une erreur inférieure à 1% sur la valeur de la résistance de poids le plus élevé correspond déjà à une erreur de 1 bit de poids le plus faible.

La précision de ce type de montage dépend principalement de la tolérance des résistances.

Pour le poids faible la valeur analogique associée vaut  $V_{REF}(R + \Delta R)/256R$ .

Si  $\Delta R/R = 1\%$  correspond à la tolérance de la résistance positionnée dans la réaction négative, alors on aurait une imprécision globale représentant 1% du bit de poids le plus faible, ce qui est insignifiant.

Pour le poids fort, la situation est plus "dramatique". La valeur analogique associée vaut  $V_{REF}(R+\Delta R)/2R$  On constate que l'imprécision générée est 128 fois plus élevée que celle du bit de poids faible. En fait l'imprécision a le même ordre de grandeur que le poids faible, ce qui signifie que le poids faible n'est pas "crédible". Seuls les 7 premiers bits seraient exploitables et ceci quelle que soit la résolution souhaitée 8, 12, 16 bits ou plus.

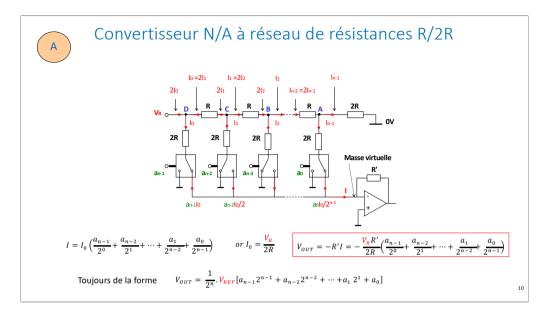

Avec le réseau R/2R proposé, le problème de l'incertitude disparaît.

Pour simplifier l'analyse, il est utile de démarrer par la droite.

Le point A voit en parallèle 2 résistances de 2R reliées respectivement à a)une masse réelle et

b)une masse réelle ou virtuelle (celle de l'A.O. en réaction négative) selon que la valeur binaire qui contrôle l'interrupteur (le switch) est à 0 ou 1.

La résistance équivalent vue depuis A vaut R et le courant entrant en A se répartit à raison d'une moitié dans chaque branche 2R.

Le point B voit en parallèle 2 résistances de 2R reliées respectivement à

a) une masse réelle et

b)une masse réelle ou virtuelle selon que la valeur binaire qui contrôle l'interrupteur est à 0 ou 1.

La résistance équivalent vue depuis B vaut R et le courant entrant en B se répartit à raison d'une moitié dans chaque branche 2R. On remarque que le courant entrant en B vaut le double du courant entrant en A.

En reformulant récursivement ces lignes, on devine aisément que le courant entrant en D est le double de celui entrant en C, qui est le double de celui entrant en B, etc... Les différentes branches qui dérivent vers l'A.O. représentent des puissances négatives de 2 (puisqu'on divise chaque fois par 2) fois un courant de référence  $I_0$ = $V_R$ /2R Cette somme de courant est

convertie en tension via l'A.O.

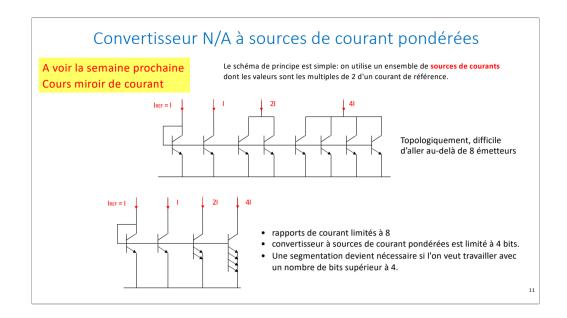

La technologie évoluant, il est possible de générer des courants pondérés grâce à des transistors structurés en "miroirs de courant".

Un miroir de courant est réalisé à partir d'un transistor de référence dont la base et le collecteur sont court-circuités (le transistor fonctionne alors toujours à la limite entre le mode linéaire et saturé).

Si la base de ce transistor est reliée à un transistor voisin dont l'émetteur est au même potentiel que celui du transistor de référence et que les deux transistors sont identiques (cela fait beaucoup de si), alors les courants de collecteur que l'on observe sont identiques ( $I_C = I_S \exp(V_{BE}/U_T)$ )

Il est possible de tirer des courants multiples du courant de référence en couplant des paires de transistors (toujours en respectant les conditions énoncées plus haut) via leurs collecteurs. Ainsi un couplage de deux transistors identiques véhiculera un courant double du courant de référence, un couplage de quatre transistors identiques véhiculera un courant quatre fois plus élevé etc...

Il est possible d'optimiser le nombre de transistors en exploitant les structures vues en TTL, à savoir les transistors multi-émetteurs.

Ainsi un double émetteurs se comportera comme un couplage de deux transistors identiques, un quadruple émetteur se comportera comme un couplage de quatre transistors identiques. On arrête cependant les structures à 8 émetteurs ce qi suppose l'artifice présenté ci-après.

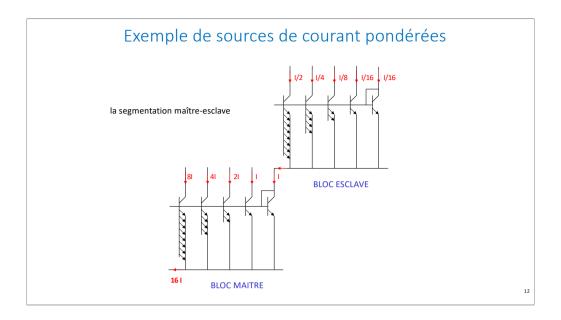

Pour pouvoir travailler sur 8 bits, il faut réaliser une segmentation des bits en deux blocs.

Le premier bloc réalisé comme précédemment, permettra de tirer à partir d'une référence  $I_{REF}$ , quatre courants pondérés:  $I_{REF}$ ,  $2I_{REF}$ ,  $4I_{REF}$  enfin  $8I_{REF}$ .

Le premier bloc complet (appelé esclave) tirera un courant total de  $I_{REF}, +I_{REF} + 2I_{REF}, +4I_{REF} + 8I_{REF} = 16I_{REF}$

Ce courant est réinjecté dans un deuxième bloc (appelé maître). Les  $16I_{REF}$  servent donc de référence pour le second bloc.

Les quatre transistors suivants généreront donc des courants valant  $16I_{REF}$ ,  $32I_{REF}$ ,  $64I_{REF}$ , enfin  $128I_{REF}$ .

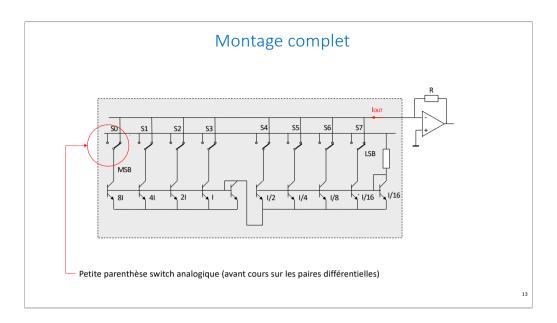

Pour avoir une structure complète, chaque source de courant est reliée à un interrupteur contrôlé par une valeur binaire. Selon la valeur binaire, le courant est extrait depuis une masse réelle (interne au circuit), ou depuis une sortie (généralement reliée à un A.O. pour réaliser une conversion courant - tension).

Le courant total extrait depuis la sortie est donc proportionnel à la valeur binaire en entrée.

Comme nous le verrons en annexe, les interrupteurs sont réalisés à partir de paires différentielles.

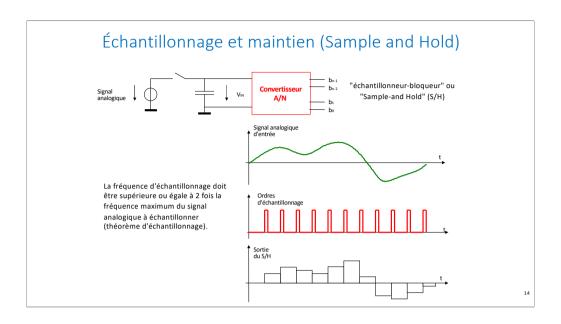

Le principe de l'échantillonnage est réalisé simplement à partir d'un interrupteur qui contrôle le chargement d'une capacité. Lorsque l'interrupteur est ouvert, la valeur présente aux bornes de la capacité est mémorisée le temps que celle-ci soit convertie en numérique. Les fréquences d'échantillonnage sont suffisamment élevées pour que la valeur stockée dans la capacité ne se dégrade pas significativement.

Comme nous l'avons évoqué dans le chapitre précédent, l'échantillonnage doit satisfaire deux contraintes:

- le temps séparant le prélèvement de deux échantillons doit permettre le traitement de l'échantillon.

- Le nombre d'échantillons prélevés doit être respectueux de la nature du signal analysé. Selon le théorème de Shannon, la fréquence d'échantillonnage doit être au minimum deux fois supérieure au signal analysé.

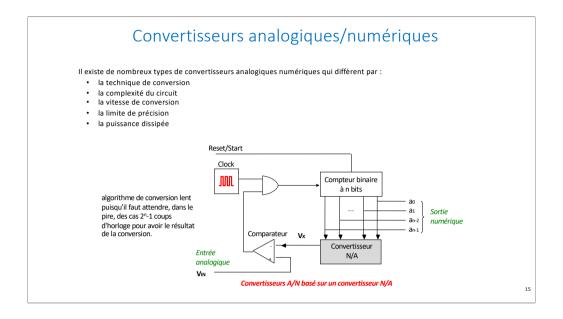

Le convertisseur CAN le plus simple est réalisé à partir d'un CNA. Le montage complet correspond à une boucle incluant quatre éléments:

- Un compteur binaire dont la sortie reflètera la valeur analogique.

- La sortie du compteur est connectée au CNA qui la convertit en une valeur analogique V<sub>X</sub>.

- Grâce à un comparateur logique, la valeur  $V_X$  est comparée à l'échantillon analogique  $V_{\rm IN}$  que l'on veut convertir en numérique.

- $\bullet$  Une porte AND permet de valider ou d'inhiber un signal d'horloge qui incrémentera le compteur. Si la valeur numérique courante (sortie du compteur) correspond à une valeur analogique inférieure à  $V_{\rm IN},$  alors le compteur continue de s'incrémenter.

Dans le pire des cas, il faudra générer 2<sup>n</sup> - 1 coups d'horloge pour atteindre la valeur recherchée.

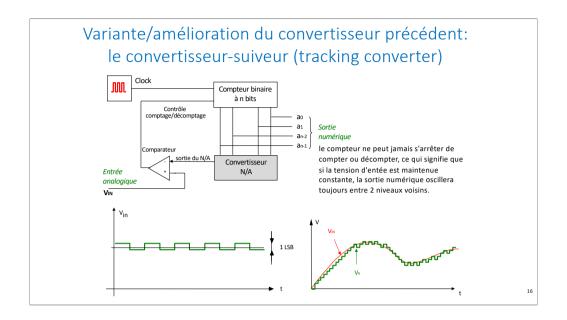

Ce convertisseur est comparable au précédent. Les caractéristiques principales sont:

- un pire cas comparable au précédent, puisqu'il serait possible d'attendre 2<sup>n</sup> 1 coups d'horloge.

- $\bullet$  Un avantage, car le compteur peut s'incrémenter ou se décrémenter, suivant mieux l'évolution du signal analogique  $V_{IN}$ .

- Un inconvénient, car une fois la valeur  $V_{\rm IN}$  atteinte, le circuit oscille autour de cette valeur, car continuellement il incrémentera ou décrémentera.

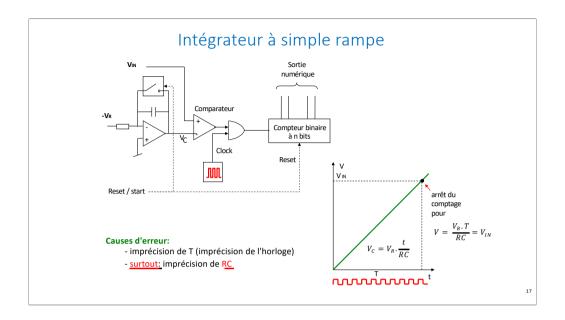

Le montage est constitué de quatre blocs:

- Un intégrateur réalisé avec un A.O. Son entrée correspond à une tension fixe  $-V_R$ . La sortie inverseuse générera donc une pente positive. A chaque début de conversion, la sortie doit être positionnée à "0", ceci est réalisé en court-circuitant la capacité.

- $\label{eq:logical_product} \begin{tabular}{ll} $\bullet$ Un comparateur logique qui produit "1" tant que $V_{\rm IN}$ (entrée analogique à convertir) est supérieure à $V_{\rm C}$ (sortie de l'intégrateur). \\ Dès que $V_{\rm C}$ dépasse $V_{\rm IN}$, le comparateur bascule à "0". \\ \end{tabular}$

- Une porte AND qui inhibe une horloge dès que  $V_{\text{C}}$  a dépassé  $V_{\text{IN}}$  ("0" à la sortie du comparateur).

- Un compteur binaire qui à chaque cycle de conversion est remis à zéro et qui s'incrémente tant que l'horloge qui le pulse reste active.

Remarque: La constante  $-V_R$  est choisie telle que, au bout de  $2^n$  - 1 coups d'horloge, la sortie ait atteint la tension max.

Le temps nécessaire pour atteindre  $V_{\rm IN}$  est donné par la loi  $V = V_R$ . T/RC. Durant ce temps,  $N_0$  coups d'horloge se sont produits générant la valeur numérique  $N_0$  à la sortie du compteur.

Le pire cas présente toujours 2<sup>n</sup> - 1 cycles. Le principal problème reste la

précision d'un tel convertisseur, sachant que T et R sont imprécises.

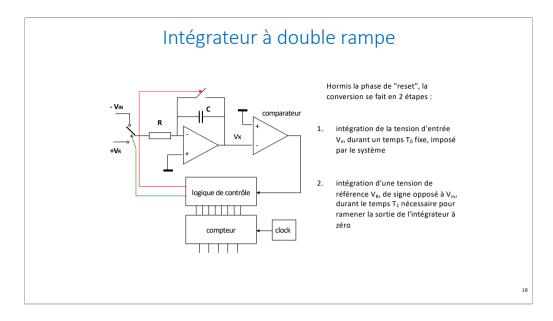

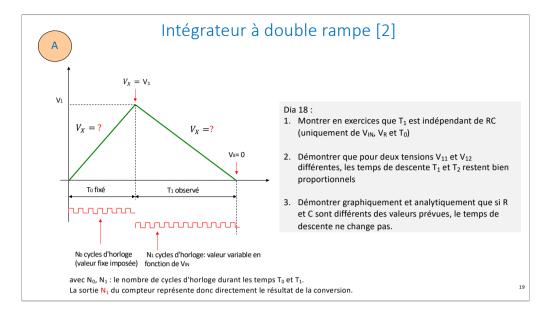

Ce circuit est plus complexe que le précédent et son comportement se décrit en deux phases. Trois blocs principaux constituent ce montage:

1) Un intégrateur traite au cours de la première phase l'entrée  $-V_{IN}$  que l'on cherche à convertir. Le temps imparti pour intégrer  $-V_{IN}$  est fixe quel que soit  $-V_{IN}$ . La tension atteinte à la fin de cette phase vaut  $V_X$  qui est donc inconnue.

Au cours d'une seconde phase, la tension  $V_R$  qui est connue est intégrée. La pente négative qui en résulte permet à la tension  $V_X$  de revenir à 0V. Si  $V_R$  et connue, en revanche, le temps nécessaire pour le retour est inconnu.

Chaque cycle de conversion commence par la mise à zéro de l'intégrateur  $(V_X\!=0)$  en court-circuitant la capacité.

- 2) le signal  $V_X$  est positionné à l'entrée du comparateur. Ce comparateur produit un "1" tant que  $V_X$  n'est pas revenu à 0V.

- 3) Durant la phase descendante de  $V_X$ , et tant que le comparateur produit un "1", le compteur reste activé et s'incrémente à chaque coup d'horloge. Au basculement à "0" du comparateur, le compteur est inhibé et la valeur à sa sorti correspond à la valeur numérique de  $V_{\rm IN}$ .

Une logique de contrôle est nécessaire pour inhiber le comptage durant la génération de la rampe positive (période connue), et pour valider le comptage durant la génération de la rampe négative (période inconnue). Cette logique doit permettre la remise à zéro de l'intégrateur à chaque nouveau cycle de

conversion.

L'analyse se déroule en deux phases:

phase 1: le temps  $T_0$  pour produire la rampe positive est connu.  $V_{\rm IN}$  étant inconnue, la pente et donc la tension atteinte  $V_X = V_{\rm IN}$ .  $T_0$  /RC sont inconnues.

phase 2: la pente  $-V_R/RC$  est connue, car  $V_R$  est connue. Le temps nécessaire pour revenir à "0" est inconnu car on démarrerait d'une tension  $V_X$  inconnue.

**Bilan**: Les deux hauteurs parcourues à l'aller et au retour sont identiques en valeur absolue, les deux expressions  $V_{IN}$ . $T_0/RC$  et  $|V_R|$ . $T_1/RC$  peuvent donc être égalisées.

Pendant T<sub>0</sub>, N<sub>0</sub> coups d'horloge sont générés

Pendant T<sub>1</sub>, N<sub>1</sub> coups d'horloge sont générés

On a directement N<sub>1</sub> qui correspond à la valeur numérique associée à V<sub>IN</sub>.

Le pire cas dans cette version met en évidence un temps pouvant être plus long (pour générer  $N_{1max}=2^n$ -1 coups d'horloge) auquel il faut évidemment rajouter  $T^0$  fixe.

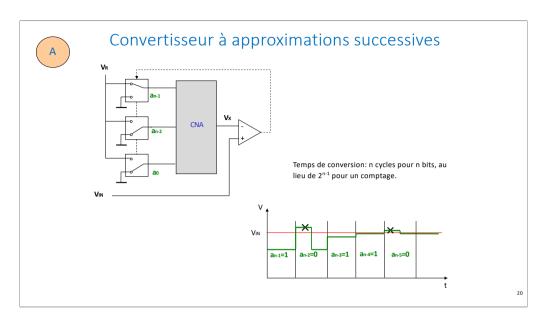

Ce type de convertisseur est beaucoup plus performant que les précédents, car le pire cas pour obtenir le résultat est directement donné par le nombre n de bits de résolution, contrairement aux cas précédents qui nécessitaient 2<sup>n</sup> - 1 coups d'horloge.

La technique se traduit par une approximation binaire successive des poids forts vers les poids faibles.

Au premier coup d'horloge, le poids fort est positionné à "1" et tous les autres bits à "0". Le poids fort correspond à la moitié de la dynamique ( $V_{MAX}/2$ ). On convertit la valeur binaire en analogique et on compare cette valeur  $V_X$  avec l'entrée  $V_{IN}$ . Si  $V_X$  est plus petite que  $V_{IN}$  on maintient le "1", sinon on repositionne la valeur à "0". La moitié du chemin a été parcourue avec ce bit. On passe ensuite au second bit de poids fort qui subit le même traitement et ainsi de suite jusqu'au bit de poids faible.

A chaque bit supplémentaire la dynamique examinée est divisée par 2.

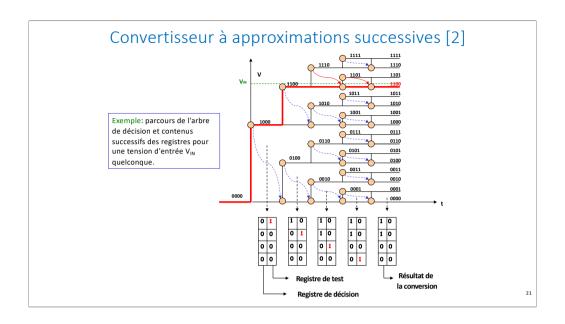

Le graphe ci-dessus nous montre tous les chemins que peut parcourir le convertisseur. C'est un parcours d'arbre binaire.

L'état des registres montre à chaque coup d'horloge l'évolution binaire du convertisseur avec maintien à "1" ou remise à "0" du bit traité.

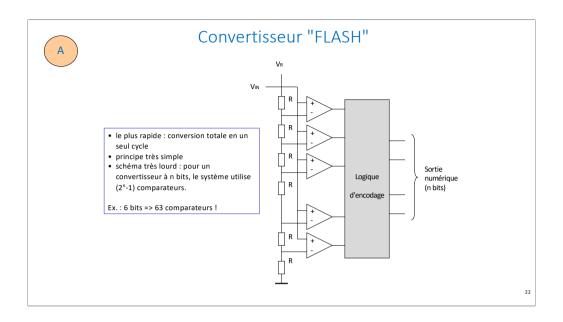

Le convertisseur Flash est de loin le plus performant car la conversion est obtenue en un coup d'horloge.

Les principe est simple:

- Une tension de référence  $V_R = V_{\rm MAX}$  est découpée en  $2^n$ -1 paliers différents grâce à un diviseur résistif contenant  $2^n$ -1 résistances.

- Chaque palier est comparé à  $V_{\rm IN}$  grâce à un comparateur logique. Il est évident que dès qu'un palier a un niveau inférieur à  $V_{\rm IN}$ , tous les paliers suivants le seront aussi.

- Il est donc nécessaire de réaliser une logique d'encodage qui détecte le premier palier inférieur à  $V_{\rm IN}$  ou si l'on préfère, le premier comparateur qui donnerait "1" en sortie. L'encodeur produit directement la valeur binaire associée à ce palier.

L'inconvénient majeur de ce circuit réside dans le volume de matériel auquel il faut consentir. Pour travailler avec 24 bits, il faudrait 16 millions de comparateurs ce qui reste impossible aujourd'hui (sans compter l'encodeur gigantesque et les 16 millions de résistances). La précision reste donc limitée.

## Les convertisseurs semi-flash.

Pour des raisons de surface, on ne réalise pas de convertisseurs flash à 8bits à cause des 255 comparateurs.

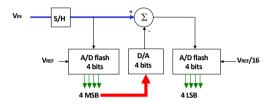

réalisation d'un convertisseur semi-flash 8 bits en utilisant 2 convertisseurs flash de 4 bits (ou 2 fois le même) à 15 comparateurs chacun.

le convertisseurs A/D flash à 4 bits doivent travailler avec une précision de 8 bits.

23

On peut améliorer la précision en travaillant avec des structures semi-flash.

Le principe est le suivant:

La valeur  $V_{\rm IN}$  est convertie via un flash sur 4 bits. Le résultat binaire est reconverti en analogique et soustrait à  $V_{\rm IN}$ . Il reste donc un résidu qui de toute évidence est au moins 16 fois inférieur à  $V_{\rm IN}$  (ordre de grandeur représentant le poids faible du 1er CAD Flash) .

Ce résidu est converti en binaire via un second flash dont la référence de tension est réadaptée à des valeurs de tension 16 fois inférieures à  $V_{\rm IN}$  (tensions résiduelles).

Le premier flash donne donc les poids forts de  $V_{\text{IN}}$  et le second flash donne les poids faibles de  $V_{\text{IN}}.$

Compte tenu des temps de propagation à travers les différents blocs (1er flash, CDA, Soustracteur, 2nd flash), ce circuit est plus lent que le précédent mas reste significativement performant.

## Résumé des performances des différents convertisseurs

### Convertisseurs A/N à intégration

- Famille de convertisseurs à plus haute résolution (16 bits et plus).

- Excellente linéarité différentielle et intégrale.

- Temps de conversion assez longs (environ 2<sup>n</sup> cycles) : ... 1ms ... 1s ...

- Applications : Instrumentation de précision.

### Convertisseurs A/N à approximations successives

- Famille de convertisseurs à moyenne résolution (8 à 14 bits).

- Temps de conversion moyens (n cycles) : 1 à 100μs

- Applications : Télécommunications

- Traitement du signal

Usages généraux.

- Bon compromis précision/vitesse/prix.

#### Convertisseurs A/N flash

- Résolution faible (4 à 8 bits).

- Temps de conversion courts (1 seul cycle) : 10ns à 1μs

Convertisseurs les plus rapides.

- Applications : radar ou Traitement numérique rapide de signaux (ex: vidéo).

L'ensemble des solutions proposées est résumé en termes de:

- Nature de convertisseur,

- précisions typiques,

- performances,

- d'applications sollicitées.